# **VRAM**

# 256K x 4 DRAM WITH 512 x 4 SAM

#### **FEATURES**

- · Industry standard pinout, timing and functions

- High performance CMOS silicon gate process

- Single +5V ±10% power supply

- Inputs and outputs are fully TTL and CMOS compatible

- Refresh modes: RAS-ONLY, CAS-BEFORE-RAS, and HIDDEN

- 512-cycle refresh within 8ms

- Optional FAST PAGE MODE access cycles

- Dual port organization: 256K x 4 DRAM port

512 x 4 SAM port

- No refresh required for Serial Access Memory

- Low power: 15mW standby; 275mW active, typical

- Fast access times 80ns random, 25ns serial

#### SPECIAL FUNCTIONS

- IEDEC Standard Function set

- PERSISTENT MASKED WRITE

- SPLIT READ TRANSFER

- WRITE TRANSFER/SERIAL INPUT

- ALTERNATE WRITE TRANSFER

# OPTIONS MARKING • Timing (DRAM, SAM) 80ns, 25ns - 8 100ns, 30ns -10 120ns, 35ns • Packages -12 Plastic SOJ DJ Plastic ZIP Z

#### GENERAL DESCRIPTION

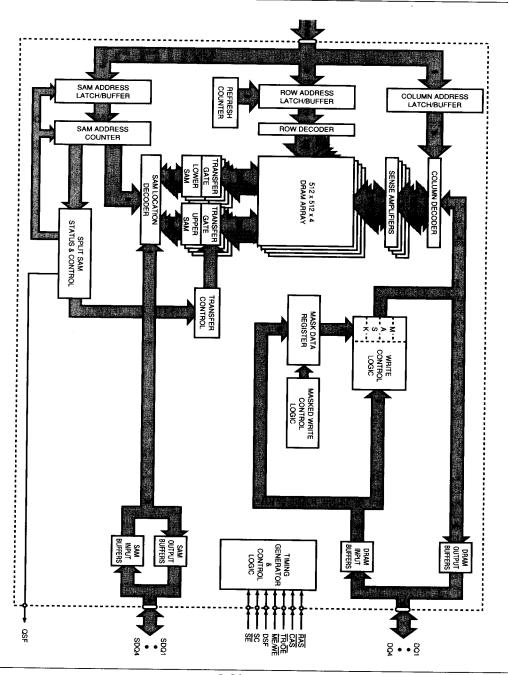

The MT42C4255 is a high speed, dual port CMOS dynamic random access memory or video RAM (VRAM) containing 1,048,576 bits. These bits may be accessed either by a 4-bit wide DRAM port or by a 512 x 4-bit serial access memory (SAM) port. Data may be transferred bidirectionally between the DRAM and the SAM.

The DRAM portion of the VRAM is functionally identical to the MT4C4256 (256K x 4-bit DRAM). Four 512-bit data registers make up the serial access memory portion of the VRAM. Data I/O and internal data transfer are accomplished using three separate bidirectional data paths: the 4-bit random access I/O port, the four internal 512 bit wide paths between the DRAM and the SAM, and the 4-bit serial I/O port for the SAM. The rest of the circuitry consists of the control, timing, and address decoding logic.

| PI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | N ASS                                               | GNME                                                                                | ENT (To                      | рV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 'iew                                      | )               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-------------------------------------------------------------------------------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-----------------|

| 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 8-Pin SC<br>(E-9)                                   | J                                                                                   | 2                            | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | in <b>Zi</b><br>:-5)                      | P               |

| SC [ 1 SD01 [ 2 SD02 [ 3 SD02 | 2 2 2 3 2 4 5 5 5 2 5 5 2 5 2 5 2 5 2 5 2 5 1 1 1 1 | 6 ] SDQ3 5 ] SE 4 ] DQ4 3 ] DQ3 2 ] DSF 1 ] CAS 0 ] QSF 9 ] A0 8 ] A1 7 ] A2 6 ] A3 | DQ2<br>NC<br>A8<br>A5<br>Vcc | 15 = 17 = 19 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 = 121 | 5 12<br>5 14<br>5 14                      | A4              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                     |                                                                                     |                              | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | =:<br>=================================== | A2<br>A0<br>CAS |

Each of the ports may be operated asynchronously and independently of the other except when data is being transferred internally between them. As with all DRAMs, the VRAM must be refreshed to maintain data. The refresh cycles must be timed so that all 512 combinations of  $\overline{RAS}$  addresses are executed at least every 8ms (regardless of sequence). Micron recommends evenly spaced refresh cycles for maximum data integrity. An internal transfer between the DRAM and the SAM counts as a refresh cycle. The SAM portion of the VRAM is fully static and does not require any refresh.

The operation and control of the MT42C4255 is compatible with (and can be identical to) the operation of the MT42C4064 (64K x 4 VRAM). However, the MT42C4255 offers several additional functions that may be used to increase system performance or ease critical timing requirements. These "special functions" are described in detail in the following section.

Micron Technology, Inc., reserves the right to change products or specifications without notice.

Figure 1 MT42C4255 BLOCK DIAGRAM

#### **PIN DESCRIPTIONS**

| SOJ PIN<br>NUMBERS                       | ZIP PIN<br>NUMBERS                       | SYMBOL      | TYPE             | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                     |

|------------------------------------------|------------------------------------------|-------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                        | 8                                        | sc          | Input            | Serial Clock: Clock input to the serial address counter for the SAM registers.                                                                                                                                                                                                                                                                                  |

| 4                                        | 11                                       | TR/OE       | Input            | Transfer Enable: Enables an internal TRANSFER operation at RAS (H → L), or  Output Enable: Enables the DRAM output buffers when taken LOW after RAS goes LOW (CAS must also be LOW), otherwise the output buffers are in the High-Z state.                                                                                                                      |

| 7                                        | 14                                       | ME/WE       | Input            | Mask Enable: If ME/WE is LOW at the falling edge of RAS a MASKED WRITE cycle is performed, or Write Enable: ME/WE is also used to select a READ (ME/WE = H) or WRITE (ME/WE = L) cycle when accessing the DRAM. This includes a READ TRANSFER (ME/WE = H) or WRITE TRANSFER (ME/WE = L).                                                                        |

| 25                                       | 4                                        | SE          | Input            | Serial Port Enable: SE enables the serial I/O buffers and allows a serial READ or WRITE operation to occur; otherwise, the output buffers are in the High-Z state. SE is also used during a WRITE TRANSFER operation to indicate whether a WRITE TRANSFER or a PSEUDO WRITE TRANSFER cycle is performed.                                                        |

| 22                                       | 1                                        | DSF         | Input            | Special Function Select: DSF is used to indicate which special functions (MASKED WRITE vs. PERSISTENT MASKED WRITE, etc.) are used on a particular access cycle.                                                                                                                                                                                                |

| 9                                        | 16                                       | RAS         | Input            | Row Address Strobe: RAS is used to clock in the 9 row-<br>address bits and as a strobe for the ME/WE, TR/OE, DSF,<br>and DQ inputs.                                                                                                                                                                                                                             |

| 21                                       | 28                                       | CAS         | Input            | Column Address Strobe: CAS is used to clock in the 9 column-address bits and enable the DRAM output buffers (DQs) (along with TR/OE).                                                                                                                                                                                                                           |

| 19, 18, 17,<br>16, 13, 12,<br>11, 15, 10 | 26, 25, 24,<br>23, 20, 19,<br>18, 22, 17 | A0 to A8    | Input            | Address Inputs: For the DRAM operation, these inputs are multiplexed and clocked by RAS and CAS to select 4 bits out of the 262,144 available. During TRANSFER operations, A0 to A8 indicate the DRAM row being accessed (when RAS goes LOW) and the SAM start address (when CAS goes LOW). A8 = "don't care" for the start address when doing SPLIT TRANSFERS. |

| 5, 6, 23, 24                             | 12, 13, 2, 3                             | DQ1 - DQ4   | input/<br>Output | DRAM Data I/O: Data Input/Output for DRAM cycles; inputs for the LOAD MASK REGISTER cycles.                                                                                                                                                                                                                                                                     |

| 2, 3, 26, 27                             | 9, 10, 5, 6                              | SDQ1 - SDQ4 | Input/<br>Output |                                                                                                                                                                                                                                                                                                                                                                 |

| 20                                       | 27                                       | QSF         | Output           | Split SAM Status: QSF indicates which half of the SAM is being accessed. LOW if address 0 to 255, HIGH if address 256 to 511.                                                                                                                                                                                                                                   |

| 8                                        | 15                                       | NC          | _                | No Connect: This pin should be left either unconnected or tied to ground.                                                                                                                                                                                                                                                                                       |

| 14                                       | 21                                       | Vcc         | Supply           | Power Supply: +5V ±10%                                                                                                                                                                                                                                                                                                                                          |

| 28                                       | 7                                        | Vss         | Supply           | Ground                                                                                                                                                                                                                                                                                                                                                          |

#### **FUNCTIONAL DESCRIPTION**

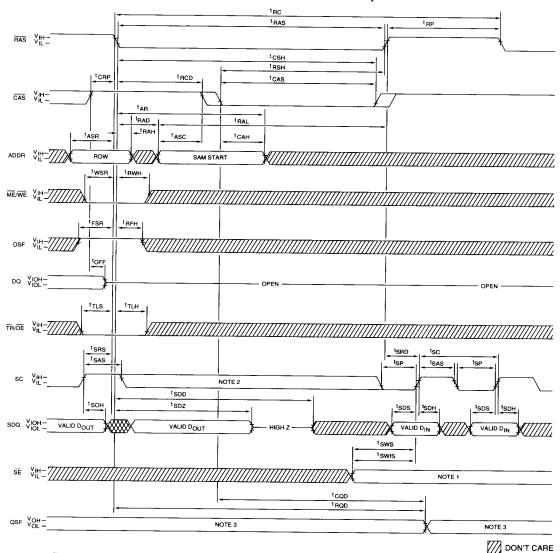

The MT42C4255 may be divided into three functional blocks (see Figure 1): the DRAM, the transfer circuitry, and the serial access memory (SAM). All of the operations described below are shown in the AC Timing Diagrams section of this data sheet and summarized in the Truth Table.

Note:

For dual function pins, the function that is not being discussed will be surrounded by parentheses. For example, when discussing transfer operations the  $\overline{TR}/\overline{OE}$  pin will be shown as  $\overline{TR}/(\overline{OE})$ .

#### **DRAM OPERATION**

#### DRAM REFRESH

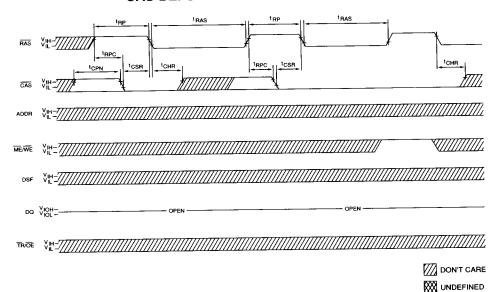

Like any DRAM based memory, the MT42C4255 VRAM must be refreshed to retain data. All 512 row-address combinations must be accessed within 8ms. The MT42C4255 supports CAS-BEFORE-RAS, RAS-ONLY and HIDDEN types of refresh cycles.

For the CAS-BÉFORE-RAS REFRESH cycle, the row addresses are generated and stored in an internal address counter. The user need not supply any address data, and simply must perform 512 CAS-BEFORE-RAS cycles within the 8ms time period.

The refresh address must be generated externally and applied to A0-A8 inputs for  $\overline{RAS}$ -ONLY REFRESH cycles. The DQ pins remain in a High-Z state for both the  $\overline{RAS}$ -ONLY and  $\overline{CAS}$ -BEFORE- $\overline{RAS}$  cycles.

HIDDEN REFRESH cycles are performed by toggling RAS (and keeping CAS LOW) after a READ or WRITE cycle. This performs CAS-BEFORE-RAS cycles but does not disturb the DQ lines.

Any DRAM READ, WRITE, or TRANSFER cycle also refreshes the DRAM row that is being accessed. The SAM portion of the MT42C4255 is fully static and does not require any refreshing.

#### DRAM READ AND WRITE CYCLES

The DRAM portion of the VRAM is nearly identical to standard 256K x 4 DRAMs. However, because several of the DRAM control pins are used for additional functions on this part, several conditions that were undefined or "don't

care" states for the DRAM are specified for the VRAM. These conditions are highlighted in the following discussion. In addition, the VRAM has several special functions that can be used when writing to the DRAM.

The 18 address bits that are used to select a 4-bit word from the 262,144 available are latched into the chip using the A0-A8, RAS and CAS inputs. First, the 9 row-address bits are set-up on the address inputs and clocked into the part when RAS transitions from HIGH to LOW. Next, the 9 column-address bits are set-up on the address inputs and clocked-in when CAS goes from HIGH to LOW.

For single port DRAMS, the  $\overline{OE}$  pin is a "don't care" when  $\overline{RAS}$  goes LOW. However, for the VRAM, when  $\overline{RAS}$  goes LOW,  $(\overline{TR})/\overline{OE}$  selects between DRAM access or TRANSFER cycles.  $(\overline{TR})/\overline{OE}$  must be HIGH at the  $\overline{RAS}$  HIGH-to-LOW transition for all DRAM operations (except  $\overline{CAS}$ -BEFORE- $\overline{RAS}$ ).

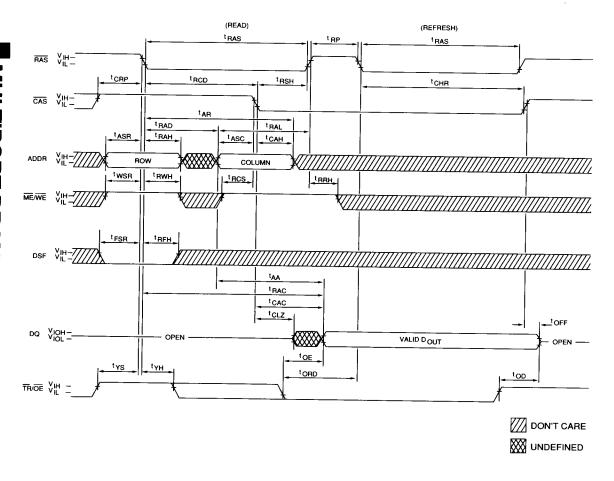

If  $(\overline{ME})/\overline{WE}$  is HIGH when  $\overline{CAS}$  goes LOW, a DRAM READ operation is performed and the data from the memory cells selected will appear at the DQ1-DQ4 port. The  $(\overline{TR})/\overline{OE}$  input must transition from HIGH to LOW sometime after  $\overline{RAS}$  falls to enable the DRAM output port.

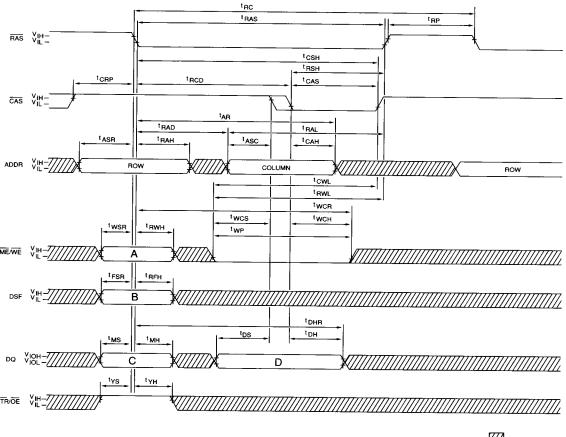

For single port normal DRAMs, WE is a "don't care" when RAS goes LOW. For the VRAM, ME/(WE) is used, when RAS goes LOW, to select between a MASKED WRITE cycle and a normal WRITE cycle. If ME/(WE) is LOW at the RAS HIGH-to-LOW transition, a MASKED WRITE operation is selected. For any DRAM access cycle (READ or WRITE), ME/(WE) must be HIGH at the RAS HIGH-to-LOW transition. If (ME)/WE is LOW before CAS goes LOW, a DRAM EARLY-WRITE operation is performed and the data present on the DQ1-DQ4 data port will be written into the selected memory cells. If (ME)/WE goes LOW after CAS goes LOW, a DRAM LATE-WRITE operation is performed. Refer to the AC timing diagrams.

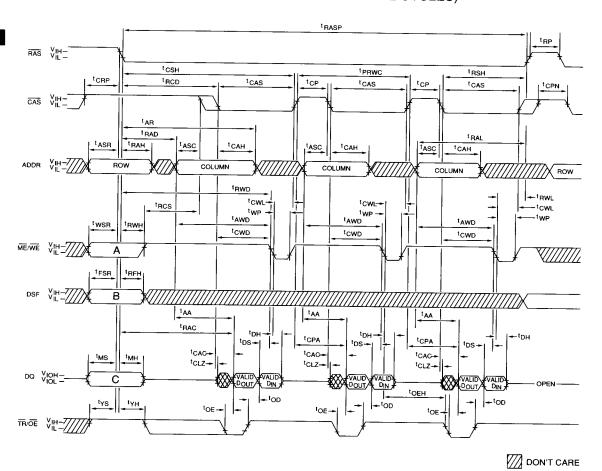

The VRAM can perform all the normal DRAM cycles including READ, EARLY-WRITE, LATE-WRITE, READ-MODIFY-WRITE, FAST-PAGE-MODE READ, FAST-PAGE-MODE WRITE (Late or Early), and FAST-PAGE-MODE READ-MODIFY-WRITE. Refer to the AC timing parameters and diagrams in the data sheet for more details on these operations.

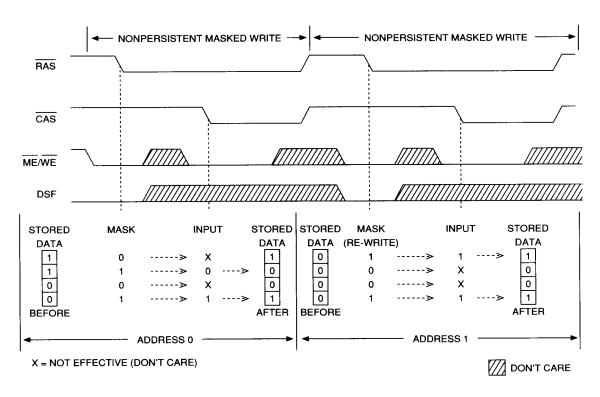

#### NONPERSISTENT MASKED WRITE

The MASKED WRITE feature eliminates the need to do a READ-MODIFY-WRITE cycle when changing only specific bits within a 4-bit word. The MT42C4255 supports two types of MASKED WRITE cycles, NONPERSISTENT MASKED WRITE and PERSISTENT MASKED WRITE.

If ME/(WE) and DSF are LOW at the RAS HIGH-to-LOW transition, a NONPERSISTENT MASKED WRITE is performed and the data (mask data) present on the DQ1-DQ4 inputs will be written into the mask data register. The mask data acts as an individual WRITE ENABLE for each of the four DQ1-DQ4 pins. If a LOW (logic "0") is written to a mask data register bit, the input port for that bit is disabled during the following WRITE operation and no new data will be written to that DRAM cell location. A HIGH (logic "1") on a mask data register bit enables the input port and allows

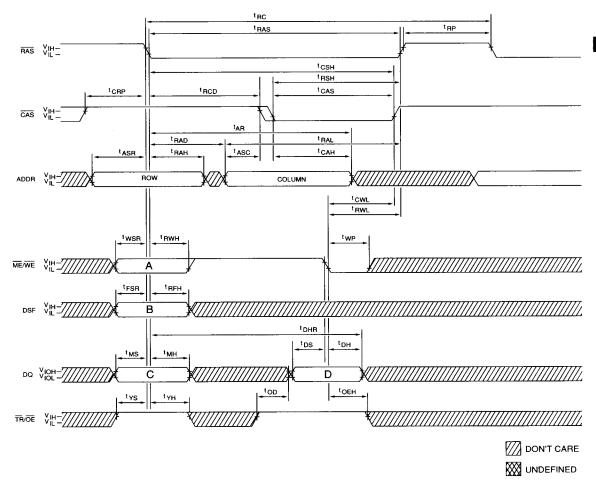

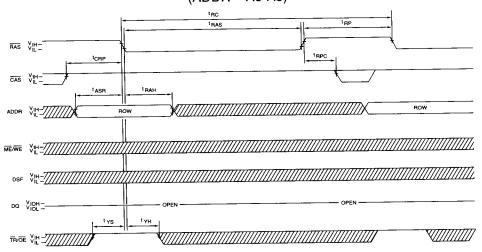

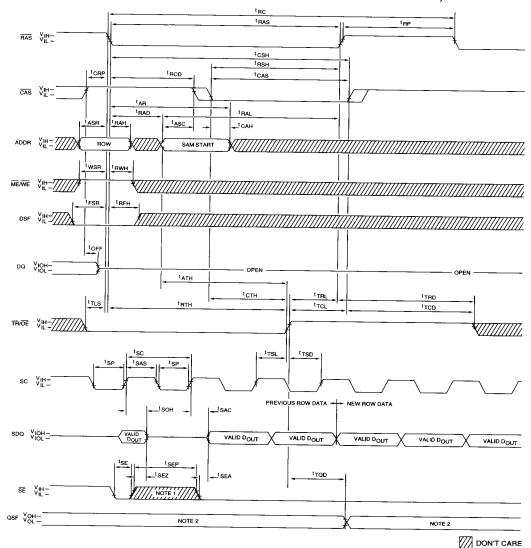

normal WRITE operation to proceed. Note that  $\overline{CAS}$  is still HIGH. When  $\overline{CAS}$  goes LOW, the bits present on the DQ1-DQ4 inputs will be either written to the DRAM (if the mask data bit is HIGH) or ignored (if the mask data bit is LOW). The DRAM contents that correspond to masked input bit will not be changed during the WRITE cycle. The MASKED WRITE is non-persistent (must be re-entered at every  $\overline{RAS}$  cycle) if DSF is LOW when  $\overline{RAS}$  goes LOW. The mask data register is cleared at the end of every NONPERSISTENT MASKED WRITE. FAST PAGE MODE can be used with NONPERSISTENT MASKED WRITE to write several column locations in an addressed row. The same mask is used during the entire FAST-PAGE-MODE  $\overline{RAS}$  cycle. An example NONPERSISTENT MASKED WRITE cycle is shown in Figure 2.

Figure 2

NONPERSISTENT MASKED WRITE EXAMPLE

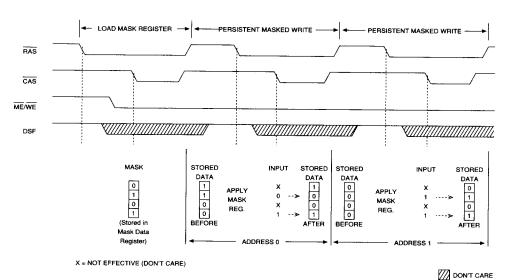

#### PERSISTENT MASKED WRITE

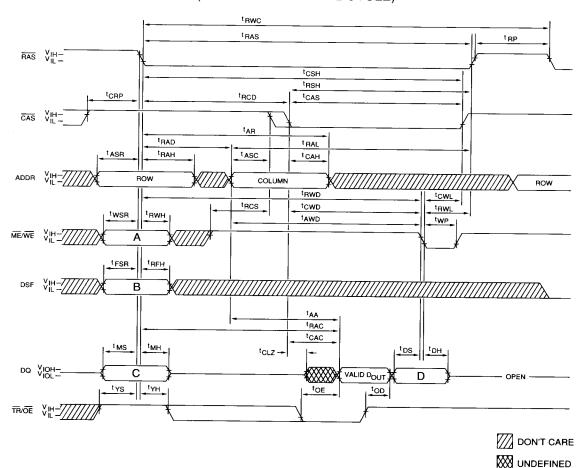

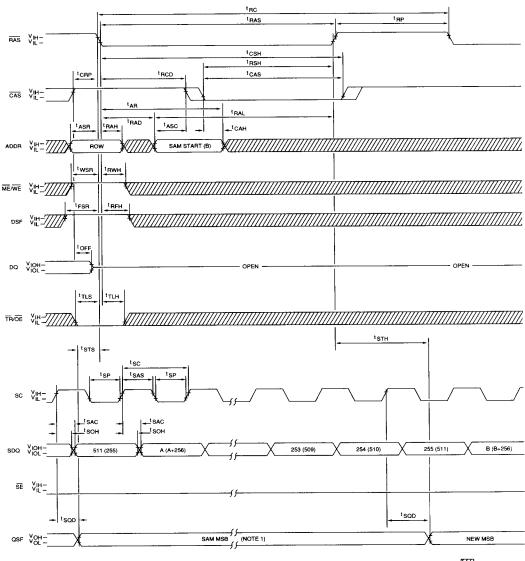

The PERSISTENT MASKED WRITE feature eliminates the need to rewrite the mask data before each MASKED WRITE cycle if the same mask data is being used repeatedly. To initiate a PERSISTENT MASKED WRITE, a LOAD MASK REGISTER cycle is performed by taking ME/(WE) and DSF HIGH when RAS goes LOW. The mask data is loaded into the internal register when CAS goes LOW. Mask data may also be loaded into the mask register by performing a NONPERSISTENT MASKED WRITE before the PERSISTENT MASKED WRITE.

PERSISTENT MASKED WRITE cycles may then be performed by taking ME/(WE) LOW and DSF HIGH when RAS goes LOW. The contents of the mask data register will then be used as the mask data for the DRAM inputs. Unlike the NONPERSISTENT MASKED WRITE, the data present on the DQ inputs is not loaded into the mask register when RAS falls, and the mask data register will not be cleared at the end of the cycle. Any number of PERSISTENT MASKED WRITE cycles, to any address, may be performed without having to reload the mask data register. Figure 3 shows the LOAD MASK REGISTER and two PERSISTENT MASKED WRITE cycles in operation. The LOAD MASK REGISTER and PERSISTENT MASKED WRITE cycles allow controllers that cannot provide mask data to the DQ pins at RAS time to perform MASKED WRITE operations. PERSISTENT MASKED WRITE operations can be performed during

FAST PAGE MODE and the same mask will apply to all addressed columns in the addressed row.

#### LOAD MASK DATA REGISTER

The LOAD MASK REGISTER operation and timing are identical to a normal WRITE cycle except that DSF is HIGH when  $\overline{RAS}$  goes LOW. As shown in the Truth Table, the combination of  $\overline{TR}/(\overline{OE})$ ,  $\overline{ME}/(\overline{WE})$ , and DSF being HIGH when  $\overline{RAS}$  goes LOW indicates the cycle is a REGISTER load cycle. DSF is used when  $\overline{CAS}$  goes LOW to select the register to be loaded and must be LOW for a LOAD MASK REGISTER cycle. The data present on the DQ lines will then be written to the mask data register.

Note: For a normal DRAM WRITE cycle, the mask data register is disabled but not modified. The contents of mask data register will not be changed unless NONPERSISTENT MASKED WRITE or LOAD MASK REGISTER cycles are performed.

The row address supplied will be refreshed, but it is not necessary to provide any particular row address. The column address inputs are ignored during a LOAD MASK REGISTER cycle.

The mask data register contents are used during PERSIS-TENT MASKED WRITE cycles to selectively enable writes to the four DQ planes.

Figure 3

PERSISTENT MASKED WRITE EXAMPLE

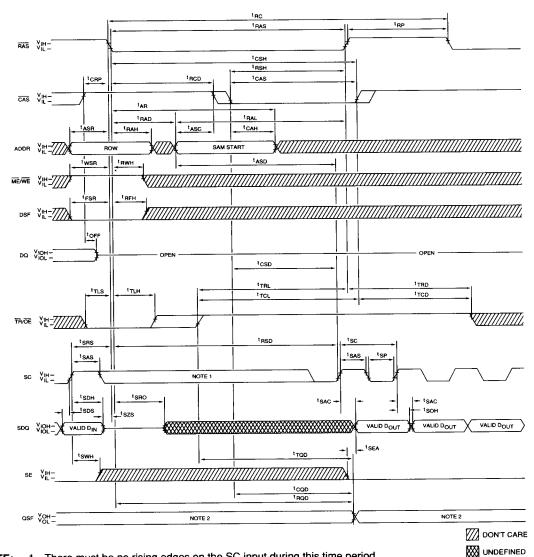

#### TRANSFER OPERATIONS

TRANSFER operations are initiated when  $\overline{TR}/(\overline{OE})$  is LOW then  $\overline{RAS}$  goes LOW. The state of  $(\overline{ME})/\overline{WE}$  when  $\overline{RAS}$  goes LOW indicates the direction of the TRANSFER (to or from the DRAM), and DSF is used to select between NORMAL TRANSFER, SPLIT READ TRANSFER, and ALTERNATE WRITE TRANSFER cycles. Each of the TRANSFER cycles available is described below.

#### READ TRANSFER (DRAM-TO-SAM TRANSFER)

If (ME)/WE is HIGH and DSF is LOW when RAS goes LOW, a READ TRANSFER cycle is selected. The row address bits indicate the four 512-bit DRAM row planes that are to be transferred to the four SAM data register planes. The column address bits indicate the start address (or Tap address) of the serial output cycle from the SAM data registers. CAS must fall for every TRANSFER in order to load a valid Tap address. A read transfer may be accom-

plished two ways. If the transfer is to be synchronized with SC (REAL-TIME READ TRANSFER), TR/(OE) is taken HIGH after CAS goes LOW. If the transfer does not have to be synchronized with SC (READTRANSFER),  $\overline{TR}/(\overline{OE})$  may go HIGH before CAS goes LOW (refer to the AC Timing Diagrams). The 2048 bits of DRAM data are written into the SAM data registers and the serial shift start address is stored in an internal 9-bit register. QSF will be LOW if access is from the lower half (addresses 0 through 255), and HIGH if access is from the upper half (256 through 511). If SE is LOW, the first bits of the new row data will appear at the serial outputs with the first SC clock pulse. SE enables the serial outputs and may be either HIGH or LOW during this operation. The SAM address pointer will increment with the SC LOW-to-HIGH transition, regardless of the state of SE. Performing a READ TRANSFER cycle sets the direction of the SAM I/O buffers to the output mode.

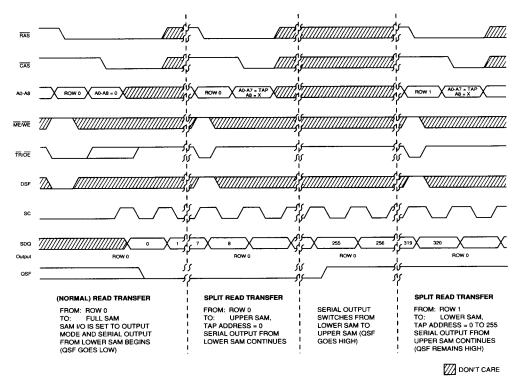

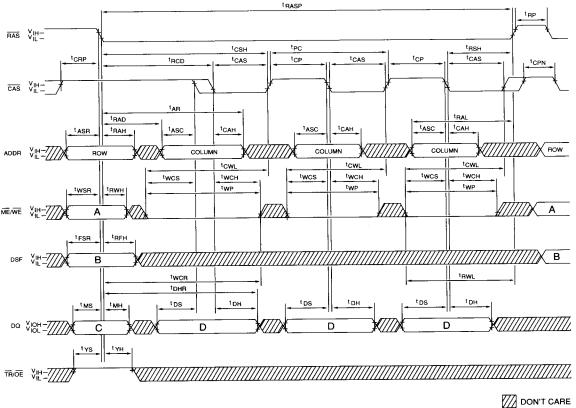

Figure 5

TYPICAL SPLIT READ TRANSFER INITIATION SEQUENCE

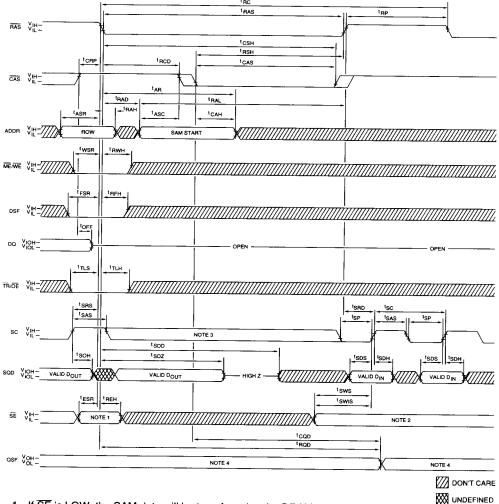

# SPLIT READ TRANSFER (SPLIT DRAM-TO-SAM TRANSFER)

The SPLIT READ TRANSFER cycle eliminates the critical transfer timing required to maintain a continuous serial output data stream. When using normal TRANSFER cycles, the REAL-TIME READ TRANSFER cycle has to occur immediately after the last bit of "old data" was clocked out of the SAM port.

When using the SPLIT TRANSFER mode, the SAM is divided into an upper half and a lower half. While data is being serially read from one half of the SAM, new DRAM data can be transferred to the other half. The transfer can occur at any time while the other half is sending data and need not be synchronized with the SC clock.

The  $\overline{TR}/(\overline{OE})$  timing is also relaxed for SPLITTRANSFER cycles. The rising edge of  $\overline{TR}/(\overline{OE})$  is not used to complete the TRANSFER cycle and therefore is independent of the rising edges of  $\overline{RAS}$  or  $\overline{CAS}$ . The transfer timing is generated internally for SPLIT TRANSFER cycles.

A normal, non-split READ TRANSFER cycle must precede any sequence of SPLIT READ TRANSFER cycles to provide a reference to which half of the SAM the access will begin. Then SPLIT READ TRANSFERS may be initiated by taking DSF HIGH when RAS goes LOW during the TRANSFER cycle. As in non-split transfers, the row address is used to specify the DRAM row to be transferred. The column address, A0-A7, is used to input the SAM Tap address. Address pin A8 is a "don't care" when the Tap address is loaded at the HIGH to LOW transition of CAS. It is internally generated so that the SPLIT TRANSFER will be to the SAM half not currently being accessed.

Figure 5 shows a typical SPLIT READ TRANSFER initiation sequence. The normal READ TRANSFER is first performed, followed by a SPLIT READ TRANSFER of the same row to the upper half of the SAM. The purpose of the SPLIT TRANSFER of the same data is to initiate the split SAM operating mode and load the Tap address. Serial access continues, and when the SAM address counter reaches 255 ("A8"=0, A0-A7=1) the new Tap address is loaded for the next half ("A8"=1, A0-A7=Tap) and the QSF output goes HIGH. Once the serial access has switched to the upper SAM, new data may be transferred to the lower SAM. The controller must wait for the state of QSF to change and then the new data may be transferred to the SAM half not being accessed. For example, the next step in Figure 5 would be to wait until QSF went LOW (indicating that row-1 data is shifting out the lower SAM) and then transfer the upper half of row 1 to the upper SAM.

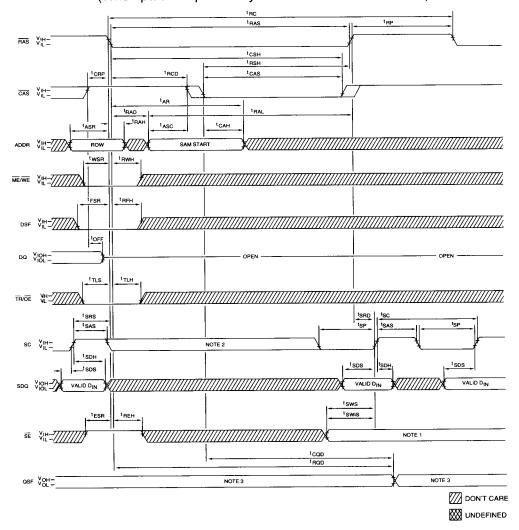

#### WRITE TRANSFER (SAM-TO-DRAM TRANSFER)

The operation of the WRITE TRANSFER is identical to the READ TRANSFER described previously, except  $(\overline{ME})/\overline{WE}$  and  $\overline{SE}$  must be LOW when  $\overline{RAS}$  goes LOW. The row address indicates the DRAM row to which the SAM data registers will be written. The column address (Tap) indicates the starting address of the next SERIAL INPUT cycle for the SAM data registers. A WRITE TRANSFER changes the direction of the SAM I/O buffers to the input mode. QFS is LOW if access is to the lower half of the SAM, and HIGH if access is to the upper half.

# PSEUDO WRITE TRANSFER (SERIAL-INPUT-MODE ENABLE)

The PSEUDO WRITE TRANSFER cycle is used to change the direction of SAM port from output to input without performing a WRITE TRANSFER cycle. A PSEUDO WRITE TRANSFER is a WRITE TRANSFER with SE held HIGH instead of LOW. The DRAM data will not be disturbed and the SAM will be ready to accept input data.

## ALTERNATE WRITE TRANSFER (SAM-TO-DRAM TRANSFER)

The operation of the ALTERNATE WRITE TRANSFER is identical to the WRITE TRANSFER except that the DSF pin is HIGH and  $(\overline{ME})/\overline{WE}$  is LOW when  $\overline{RAS}$  goes LOW, allowing  $\overline{SE}$  to be a "don't care." This allows the outputs to be disabled using  $\overline{SE}$  during a WRITE TRANSFER cycle.

#### POWER UP AND INITIALIZATION

When Vcc is initially supplied or when refresh is interrupted for more than 8ms, the MT42C4255 must be initialized.

After Vcc is at specified operating conditions, for 100 $\mu$ s minimum, 8  $\overline{RAS}$  cycles and 1 SC cycle must be executed to initialize the memory array. When the device is initialized, the DRAM I/O pins (DQs) are in a High-Z state, regardless of the state of  $(\overline{TR})/\overline{OE}$ . The DRAM array will contain random data.

The SAM portion of the MT42C4255 is completely static in operation and does not require refresh or initialization. The SAM port will power-up in the serial input mode (WRITE TRANSFER) and the I/O pins (SDQ's) will be High-Z, regardless of the state of SEa,b. The mask register will contain random data after power-up.

4 0

# **MULTIPORT DRAM**

# TRUTH TABLE

| 3000 | FUNCTION                                          |     | 팷     | RAS FALLING EDGE | EDGE |     | A0 - A81         | A81    | DQ1 - DQ42 | DQ4 <sup>2</sup> |               |

|------|---------------------------------------------------|-----|-------|------------------|------|-----|------------------|--------|------------|------------------|---------------|

|      |                                                   | CAS | TR/OE | ME/WE            | DSF  | 318 | RAS              | A8=X   | RAS        | CAS <sup>3</sup> | MASK REGISTER |

|      | DRAM OPERATIONS                                   |     |       |                  |      |     |                  |        |            |                  |               |

| CBR  | CAS-BEFORE-FAS REFRESH                            | ٥   | ×     | ×                | ×    | ×   | ı                | ×      | ŀ          | ×                | ×             |

| R    | RAS-ONLY REFRESH                                  | -   | -     | ×                | ×    | ×   | ROW              | ı      | ×          | ı                | ×             |

| ₽₩   | NORMAL DRAM READ OR WRITE                         | -   | -     | 1                | 0    | ×   | ROW              | COLUMN | ×          | VALID<br>DATA    | ×             |

| RWNM | NONPERSISTENT (LOAD AND USE) MASKED WRITE TO DRAM | 1   | _     | 0                | 0    | ×   | MOB              | COLUMN | WRITE      | VALID<br>DATA    | asn<br>% dvon |

| RWOM | PERSISTENT (USE REGISTER) MASKED WRITE TO DRAM    | 1   | 1     | 0                | _    | ×   | ROW              | COLUMN | ×          | VALID<br>DATA    | USE           |

|      | REGISTER OPERATIONS                               |     |       |                  |      |     |                  |        |            |                  |               |

| LMR  | LOAD MASK REGISTER                                | 1   | -     | 1                | _    | ×   | ROW <sup>4</sup> | ×      | ×          | WRITE            | LOAD          |

|      | TRANSFER OPERATIONS                               |     |       |                  |      |     |                  |        |            |                  |               |

| 꼭    | READ TRANSFER (DRAM-TO-SAM TRANSFER)              | _   | 0     | _                | 0    | ×   | ROW              | TAPs   | ×          | ×                | ×             |

| SRT  | SPLIT READ TRANSFER (SPLIT DRAM-TO-SAM TRANSFER)  | -   | 0     | _                | 1    | ×   | MOH              | TAPs   | ×          | ×                | ×             |

| \$   | WRITE TRANSFER (SAM-TO-DRAM TRANSFER)             | -   | 0     | 0                | 0    | 0   | ROW              | ТАР    | ×          | ×                | ×             |

| PWT  | PSEUDO WRITE TRANSFER (SERIAL-INPUT-MODE ENABLE)  | -   | 0     | 0                | ۰    | _   | ROW4             | TAPs   | ×          | ×                | ×             |

| AWT  | ALTERNATE WRITE TRANSFER (SAM-TO-DRAM TRANSFER)   | _   | 0     | 0                | _    | ×   | ROW              | TAPs   | ×          | ×                | ×             |

- NOTE: 1. These columns show what must be present on the A0-A8 inputs when RAS falls and when CAS falls.

- These columns show what must be present on the DQ1-DQ4 inputs when AAS falls and when CAS falls.

- On WRITE cycles, the input data is latched at the falling edge of CAS or ME/WE, whichever is later. Similarly, on READ cycles, the output data is latched at the falling edge of CAS or TR/OE, whichever is later

- The ROW that is addressed will be refreshed, but no particular ROW address is required.

- This is the first SAM address location that the first SC cycle will access. For Split SAM transfers, the Tap reached (255 for lower half, 511 for upper half). will be the first address location accessed of the "new" SAM half after the boundary of the current half is

#### **ABSOLUTE MAXIMUM RATINGS\***

| Voltage on Vcc supply relative to Vss | 1.0V to +7.0V  |

|---------------------------------------|----------------|

| Operating Temperature, Ta(Ambient)    |                |

| Storage Temperature (Plastic)         | 55°C to +150°C |

| Power Dissipation                     | 1 W            |

| Short Circuit Output Current          |                |

\*Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

#### RECOMMENDED DC OPERATING CONDITIONS

$(0^{\circ}C \leq T_{{\color{blue}A}} \leq 70^{\circ}C)$

| PARAMETER/CONDITION                      | SYMBOL | MIN  | MAX   | UNITS | NOTES |

|------------------------------------------|--------|------|-------|-------|-------|

| Supply Voltage                           | Vcc    | 4.5  | 5.5   | ٧     | 1     |

| Input High (Logic 1) Voltage, All Inputs | Vih    | 2.4  | Vcc+1 | V     | 1     |

| Input Low (Logic 0) Voltage, All Inputs  | ViL    | -1.0 | 0.8   | ٧     | 1     |

#### DC ELECTRICAL CHARACTERISTICS

$(0^{\circ}C \le T_{A} \le 70^{\circ}C; Vcc = 5.0V \pm 10\%)$

| PARAMETER/CONDITION                                                                | SYMBOL | MIN | MAX | UNITS | NOTES |

|------------------------------------------------------------------------------------|--------|-----|-----|-------|-------|

| INPUT LEAKAGE CURRENT (any input (0V≤VIN≤Vcc), all other pins not under test = 0V) | IL     | -10 | 10  | μА    |       |

| OUTPUT LEAKAGE CURRENT<br>(DQ, SDQ disabled, 0V≤Vouт≤Vcc)                          | loz    | -10 | 10  | μА    |       |

| OUTPUT LEVELS Output High Voltage (Iout = -2.5mA)                                  | Vон    | 2.4 |     | V     |       |

| Output Low Voltage (Iout = 5mA)                                                    | Vol    |     | 0.4 | l v   | 1     |

#### **CAPACITANCE**

| PARAMETER                                              | SYMBOL | MIN | MAX | UNITS | NOTES |

|--------------------------------------------------------|--------|-----|-----|-------|-------|

| Input Capacitance: A0-A8                               | Cıı    |     | 5   | pF    | 2     |

| Input Capacitance: RAS, CAS, ME/WE, TR/OE, SC, SE, DSF | Cı2    |     | 8   | pF    | 2     |

| Input/Output Capacitance: DQ, SDQ                      | Ci/o   |     | 9   | pF    | 2     |

| Output Capacitance: QSF                                | Co     |     | 9   | pF    | 2     |

# CURRENT DRAIN, SAM IN STANDBY $(0^{\circ}C \le T_{A} \le 70^{\circ}C; \ Vcc = 5.0V \pm 10\%)$

| $0^{\circ}C \le T_{A} \le 70^{\circ}C; \ Vcc = 5.0V \pm 10\%)$                                      |        |    | MAX |     | ]     |       |

|-----------------------------------------------------------------------------------------------------|--------|----|-----|-----|-------|-------|

| PARAMETER/CONDITION                                                                                 | SYMBOL | -8 | -10 | -12 | UNITS | NOTES |

| OPERATING CURRENT (RAS and CAS = Cycling: <sup>t</sup> RC = <sup>t</sup> RC (MIN))                  | Icc1   | 90 | 80  | 70  | mA    | 3, 4  |

| OPERATING CURRENT: FAST PAGE MODE (RAS = Vil.; CAS = Cycling: ¹PC = ¹PC (MIN))                      | Icc2   | 70 | 60  | 50  | mA    | 3, 4  |

| STANDBY CURRENT: TTL INPUT LEVELS Power supply standby current (RAS=CAS=VIH after 8 RAS cycles min) | Іссз   | 10 | 10  | 10  | mA    |       |

| REFRESH CURRENT: RAS-ONLY<br>(RAS-Cycling; CAS-ViH)                                                 | łcc4   | 90 | 80  | 70  | mA    | 3     |

| REFRESH CURRENT: CAS-BEFORE-RAS (RAS and CAS=Cycling)                                               | lcc5   | 80 | 70  | 60  | mA    | 3, 5  |

| SAM/DRAM DATA TRANSFER                                                                              | Icc6   | 95 | 85  | 75  | mA    | 3     |

# CURRENT DRAIN, SAM ACTIVE ( $^{\dagger}$ SC = MIN) ( $0^{\circ}$ C $\leq T_{A} \leq 70^{\circ}$ C; $V_{CC} = 5.0V \pm 10\%$ )

| $(0.0 \le 1_A \le 70.0; \text{ VCC} = 5.0 \text{ V} \pm 10\%)$                                        |        |     | MAX |     |       |         |

|-------------------------------------------------------------------------------------------------------|--------|-----|-----|-----|-------|---------|

| PARAMETER/CONDITION                                                                                   | SYMBOL | -8  | -10 | -12 | UNITS | NOTES   |

| OPERATING CURRENT (RAS and CAS = Cycling: <sup>t</sup> RC = <sup>t</sup> RC (MIN))                    | Icc7   | 130 | 120 | 110 | mA    | 3, 4    |

| OPERATING CURRENT: FAST PAGE MODE (RAS = VIL; CAS = Cycling: <sup>t</sup> PC = <sup>t</sup> PC (MIN)) | Iccs   | 110 | 100 | 90  | mA    | 3, 4    |

| STANDBY CURRENT: TTL INPUT LEVELS Power supply standby current (RAS=CAS=VIH after 8 RAS cycles min)   | lcc9   | 50  | 45  | 40  | mA    | 3, 4    |

| REFRESH CURRENT: RAS-ONLY<br>(RAS=Cycling; CAS=Vін)                                                   | Icc10  | 130 | 120 | 110 | mA    | 3, 4    |

| REFRESH CURRENT: CAS-BEFORE-RAS (RAS and CAS=Cycling)                                                 | Icc11  | 120 | 110 | 100 | mA    | 3, 4, 5 |

| SAM/DRAM DATA TRANSFER                                                                                | ICC12  | 135 | 125 | 115 | mA    | 3, 4    |

#### **DRAM TIMING PARAMETERS**

#### **ELECTRICAL CHARACTERISTICS AND RECOMMENDED AC OPERATING CONDITIONS**

(Notes: 6, 7, 8, 9, 10, 11, 12, 13) (0°C  $\leq$  T<sub>A</sub>  $\leq$  +70°C; Vcc = 5.0V  $\pm$  10%)

| A.C. CHARACTERISTICS                         |                   |     | -8      | -   | 10      | _   | 12       |       |        |

|----------------------------------------------|-------------------|-----|---------|-----|---------|-----|----------|-------|--------|

| PARAMETER                                    | SYM               | MIN | MAX     | MIN | MAX     | MIN | MAX      | UNITS | NOTES  |

| Random READ or WRITE cycle time              | t <sub>RC</sub>   | 150 |         | 180 |         | 210 |          | ns    |        |

| READ-MODIFY-WRITE cycle time                 | <sup>t</sup> RWC  | 205 |         | 235 |         | 280 |          | ns    |        |

| FAST-PAGE-MODE READ or WRITE                 | <sup>t</sup> PC   | 45  |         | 55  |         | 65  |          | ns    |        |

| cycle time                                   |                   |     |         |     |         |     |          |       |        |

| FAST-PAGE-MODE READ-MODIFY-WRITE             | tPRWC             | 100 |         | 110 |         | 140 |          | ns    |        |

| cycle time                                   |                   |     |         |     |         |     | <u> </u> |       |        |

| Access time from RAS                         | t <sub>RAC</sub>  |     | 80      |     | 100     |     | 120      | ns    | 14     |

| Access time from CAS                         | t <sub>CAC</sub>  |     | 25      |     | 30      |     | 35       | ns    | 15     |

| Access time from (TR)/OE                     | t <sub>OE</sub>   |     | 20      |     | 25      |     | 30       | ns    |        |

| Access time from column address              | t <sub>AA</sub>   |     | 40      |     | 50      |     | 60       | ns    |        |

| Access time from CAS precharge               | <sup>t</sup> CPA  |     | 45      |     | 55      |     | 65       | ns    |        |

| RAS pulse width                              | <sup>t</sup> RAS  | 80  | 10,000  | 100 | 10,000  | 120 | 10,000   | ns    |        |

| RAS pulse width (FAST PAGE MODE)             | t <sub>RASP</sub> | 80  | 100,000 | 100 | 100,000 | 120 | 100,000  | ns    |        |

| RAS hold time                                | <sup>t</sup> RSH  | 25  |         | 30  |         | 35  |          | ns    |        |

| RAS precharge time                           | t <sub>RP</sub>   | 60  |         | 70  |         | 80  |          | ns    |        |

| CAS pulse width                              | t <sub>CAS</sub>  | 25  | 10,000  | 30  | 10,000  | 35  | 10,000   | ns    |        |

| CAS hold time                                | t <sub>CSH</sub>  | 80  |         | 100 |         | 120 |          | ns    |        |

| CAS precharge time                           | <sup>t</sup> CPN  | 15  |         | 15  |         | 20  |          | ns    | 16     |

| CAS precharge time (FAST PAGE MODE)          | <sup>t</sup> CP   | 10  |         | 10  |         | 15  |          | ns    |        |

| RAS to CAS delay time                        | tRCD              | 20  | 55      | 20  | 70      | 25  | 85       | ns    | 17     |

| CAS to RAS precharge time                    | tCRP              | 5   |         | 5   |         | 10  |          | ns    |        |

| Row address setup time                       | t <sub>ASR</sub>  | 0   |         | 0   |         | 0   |          | ns    |        |

| Row address hold time                        | <sup>t</sup> RAH  | 12  |         | 15  |         | 15  |          | ns    |        |

| RAS to column                                | <sup>t</sup> RAD  | 17  | 40      | 20  | 50      | 20  | 60       | ns    | 18     |

| address delay time                           |                   |     |         |     |         |     |          |       |        |

| Column address setup time                    | tASC              | 0   | [ T     | 0   |         | 0   |          | ns    |        |

| Column address hold time                     | t <sub>CAH</sub>  | 20  |         | 20  |         | 25  |          | пѕ    |        |

| Column address hold time                     | t <sub>AR</sub>   | 60  |         | 70  |         | 85  |          | ns    |        |

| (referenced to RAS)                          |                   |     |         |     |         |     |          |       |        |

| Column address to                            | t <sub>RAL</sub>  | 40  |         | 50  |         | 60  |          | ns    |        |

| RAS lead time                                |                   |     |         |     |         |     |          |       |        |

| Read command setup time                      | t <sub>RCS</sub>  | 0   |         | 0   |         | 0   |          | ns    |        |

| Read command hold time                       | <sup>t</sup> RCH  | 0   |         | 0   |         | 0   | 1        | ns    | 19     |

| (referenced to CAS)                          |                   |     |         |     |         |     |          |       |        |

| Read command hold time                       | t <sub>RRH</sub>  | 0   |         | 0   |         | 0   |          | ns    | 19     |

| (referenced to RAS)                          |                   |     |         |     |         | •   |          |       |        |

| CAS to output in Low-Z                       | t <sub>CLZ</sub>  | 0   |         | 0   |         | 0   | 1        | ns    |        |

| Output buffer turn-off delay                 | <sup>t</sup> OFF  | 0   | 20      | 0   | 20      | 0   | 30       | ns    | 20, 23 |

| Output Disable                               | dO <sup>t</sup>   | 0   | 20      | 0   | 20      | 0   | 30       | ns    | 23     |

| Output Disable hold time from start of write | tOEH              |     | 15      |     | 15      |     | 20       | ns    | 27     |

| Output Enable to RAS delay                   | <sup>t</sup> ORD  |     | 0       |     | 0       |     | 0        | ns    |        |

#### **DRAM TIMING PARAMETERS (Continued)**

#### **ELECTRICAL CHARACTERISTICS AND RECOMMENDED AC OPERATING CONDITIONS**

(Notes: 6, 7, 8, 9, 10, 11, 12, 13) (0°C  $\leq T_A \leq +70$ °C; Vcc = 5.0V  $\pm$  10%)

| A.C. CHARACTERISTICS                        |                  | _   | 8   |     | 10  | -1  | 12  |       |       |

|---------------------------------------------|------------------|-----|-----|-----|-----|-----|-----|-------|-------|

| PARAMETER                                   | SYM              | MIN | MAX | MIN | MAX | MIN | MAX | UNITS | NOTES |

| Write command setup time                    | twcs             | 0   |     | 0   |     | 0   |     | ns    | 21    |

| Write command hold time                     | twch             | 15  |     | 20  |     | 25  |     | ns    |       |

| Write command hold time (referenced to RAS) | twcr             | 60  |     | 70  |     | 85  |     | ns    |       |

| Write command pulse width                   | tWP              | 15  |     | 15  |     | 20  |     | ns    |       |

| Write command to RAS lead time              | <sup>t</sup> RWL | 20  |     | 20  |     | 25  |     | ns    |       |

| Write command to CAS lead time              | t <sub>CWL</sub> | 20  |     | 20  |     | 25  |     | ns    |       |

| Data-in setup time                          | t <sub>DS</sub>  | 0   |     | 0   |     | 0   |     | ns    | 22    |

| Data-in hold time                           | t <sub>DH</sub>  | 20  |     | 20  |     | 25  |     | ns    | 22    |

| Data-in hold time<br>(referenced to RAS)    | <sup>t</sup> DHR | 60  |     | 70  |     | 90  |     | ns    |       |

| RAS to WE delay time                        | t <sub>RWD</sub> | 110 |     | 130 |     | 160 |     | ns    | 21    |

| Column address<br>to WE delay time          | <sup>t</sup> AWD | 70  |     | 80  |     | 100 |     | ns    | 21    |

| CAS to WE delay time                        | tcwD             | 55  |     | 60  |     | 65  |     | ns    | 21    |

| Transition time (rise or fall)              | t <sub>T</sub>   | 3   | 50  | 3   | 50  | 3   | 50  | ns    | 9, 10 |

| Refresh period (512 cycles)                 | t <sub>REF</sub> |     | 8   |     | 8   |     | 8   | ms    |       |

| RAS to CAS precharge time                   | <sup>t</sup> RPC | 0   |     | 0   |     | 0   |     | ns    |       |

| CAS setup time<br>(CAS-BEFORE-RAS REFRESH)  | <sup>t</sup> CSR | 10  |     | 10  |     | 10  |     | ns    | 5     |

| CAS hold time<br>(CAS-BEFORE-RAS REFRESH)   | <sup>t</sup> CHR | 30  |     | 30  |     | 30  |     | ns    | 5     |

| ME/WE to RAS setup time                     | twsn             | 0   |     | 0   |     | 0   |     | ns    |       |

| ME/WE to RAS hold time                      | <sup>t</sup> RWH | 12  |     | 15  |     | 15  |     | ns    | T     |

| Mask Data to RAS setup time                 | t <sub>MS</sub>  | 0   |     | 0   |     | 0   |     | ns    |       |

| Mask Data to RAS hold time                  | <sup>t</sup> MH  | 12  |     | 15  |     | 15  |     | ns    |       |

### TRANSFER AND MODE CONTROL TIMING PARAMETERS ELECTRICAL CHARACTERISTICS AND RECOMMENDED AC OPERATING CONDITIONS (Notes 6, 7, 8, 9, 10) (0° C $\leq$ T<sub>A</sub> $\leq$ + 70°C; Vcc = 5.0V $\pm$ 10%)

| A.C. CHARACTERISTICS                                                            |                  |     | -8     |     | 10     | -   | 12       | L     | Щ.    |

|---------------------------------------------------------------------------------|------------------|-----|--------|-----|--------|-----|----------|-------|-------|

| PARAMETER                                                                       | SYM              | MIN | MAX    | MIN | MAX    | MIN | MAX      | UNITS | NOTES |

| TRANSFER command to RAS setup time                                              | t <sub>TLS</sub> | 0   |        | 0   |        | 0   |          | ns    | 25    |

| TRANSFER command to RAS hold time                                               | <sup>t</sup> TLH | 12  | 10,000 | 15  | 10,000 | 15  | 10,000   | ns    | 25    |

| TRANSFER command to RAS hold time (REAL-TIME READ TRANSFER only)                | <sup>t</sup> RTH | 70  | 10,000 | 80  | 10,000 | 90  | 10,000   | ns    | 25    |

| TRANSFER command to CAS hold time (REAL-TIME READ TRANSFER only)                | t <sub>CTH</sub> | 20  |        | 25  |        | 30  |          | ns    | 25    |

| TRANSFER command to column address hold time (for REAL TIME READ TRANSFER only) | tATH             | 25  |        | 30  |        | 35  |          | ns    | 25    |

| TRANSFER command to SC lead time                                                | tTSL             | 5   |        | 5   |        | 5   |          | ns    | 25    |

| TRANSFER command to RAS lead time                                               | tTRL             | 0   |        | 0   |        | 0   |          | ns    | 25    |

| TRANSFER command to RAS delay time                                              | <sup>t</sup> TRD | 15  |        | 15  |        | 15  |          | ns    | 25    |

| TRANSFER command to CAS time                                                    | <sup>†</sup> TCL | 0   |        | 0   |        | 0   | <u> </u> | ns    | 25    |

| TRANSFER command to CAS delay time                                              | tTCD             | 15  |        | 15  |        | 15  |          | ns    | 25    |

| First SC edge to TRANSFER command delay time                                    | t <sub>TSD</sub> | 10  |        | 10  |        | 10  |          | ns    | 25    |

| Serial output buffer turn-off delay from RAS                                    | <sup>t</sup> SDZ | 10  | 35     | 10  | 40     | 10  | 50       | ns    |       |

| SC to RAS setup time                                                            | t <sub>SRS</sub> | 30  |        | 30  |        | 40  |          | ns    |       |

| RAS to SC delay time                                                            | t <sub>SRD</sub> | 20  |        | 25  |        | 30  |          | ns    |       |

| Serial data input to SE delay time                                              | t <sub>SZE</sub> | 0   |        | 0   |        | 0   |          | ns    |       |

| RAS to SD buffer turn-on time                                                   | t <sub>SRO</sub> | 10  |        | 15  |        | 15  |          | ns    |       |

| Serial data input delay from RAS                                                | t <sub>SDD</sub> | 45  |        | 50  |        | 55  |          | ns    |       |

| Serial data input to RAS delay time                                             | t <sub>SZS</sub> | 0   |        | 0   |        | 0   |          | ns    |       |

| Serial-input-mode enable (SE) to RAS setup time                                 | <sup>t</sup> ESR | 0   |        | 0   |        | 0   |          | ns    |       |

| Serial-input-mode enable<br>(SE) to RAS hold time                               | <sup>t</sup> REH | 12  |        | 15  |        | 15  |          | ns    |       |

| NONTRANSFER command to RAS setup time                                           | t <sub>YS</sub>  | 0   |        | 0   |        | 0   |          | ns    | 26    |

| NONTRANSFER command to RAS hold time                                            | t <sub>Y</sub> H | 12  |        | 15  |        | 15  |          | ns    | 26    |

| DSF to RAS setup time                                                           | t <sub>FSR</sub> | 0   |        | 0   |        | 0   |          | ns    |       |

| DSF to RAS hold time                                                            | t <sub>RFH</sub> | 12  |        | 15  |        | 15  |          | ns    |       |

| SC to QSF delay time                                                            | tsQD             |     | 25     |     | 30     |     | 35       | ns    |       |

| SPLIT TRANSFER setup time                                                       | tSTS             | 30  |        | 35  |        | 40  |          | ns    |       |

| SPLIT TRANSFER hold time                                                        | t <sub>STH</sub> | 30  |        | 35  |        | 40  |          | ns    |       |

| RAS to QSF delay time                                                           | t <sub>RQD</sub> |     | 65     |     | 85     |     | 105      | ns    |       |

| TR/OE to QSF delay time                                                         | <sup>t</sup> TQD |     | 25     |     | 30     |     | 35       | ns    |       |

| CAS to QSF delay time                                                           | tCQD             |     | 35     |     | 40     |     | 45       | ns    |       |

| RAS to first SC delay                                                           | <sup>t</sup> RSD | 80  |        | 95  |        | 105 |          | ns    |       |

| CAS to first SC delay                                                           | tCSD             | 20  |        | 25  |        | 35  |          | ns    |       |

| Column address valid to first SC delay                                          | tASD             | 45  |        | 55  |        | 65  |          | ns    |       |

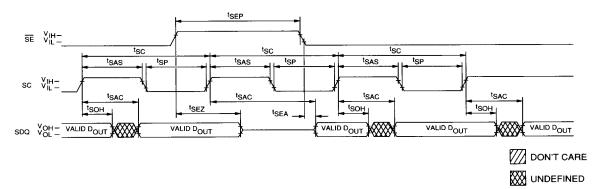

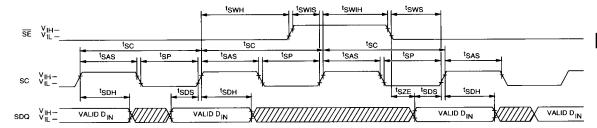

#### **SAM TIMING PARAMETERS**

#### **ELECTRICAL CHARACTERISTICS AND RECOMMENDED AC OPERATING CONDITIONS**

(Notes 6, 7, 8, 9, 10) (0° C  $\leq$  T<sub> $\Delta$ </sub>  $\leq$  + 70°C; Vcc = 5.0V  $\pm$  10%)

| A.C. CHARACTERISTICS                        |                   | -8  |     | -10 |     | -12 |     |       | i     |

|---------------------------------------------|-------------------|-----|-----|-----|-----|-----|-----|-------|-------|

| PARAMETER                                   | SYM               | MIN | MAX | MIN | MAX | MIN | MAX | UNITS | NOTES |

| Serial clock cycle time                     | tsc tsc           | 25  |     | 30  |     | 35  |     | ns    |       |

| Access time from SC                         | t <sub>SAC</sub>  |     | 25  |     | 30  |     | 35  | ns    | 24    |

| SC precharge time (SC LOW time)             | t <sub>SP</sub>   | 10  |     | 10  |     | 12  |     | ns    |       |

| SC pulse width (SC HIGH time)               | t <sub>SAS</sub>  | 10  |     | 10  |     | 12  |     | ns    |       |

| Access time from SE                         | tSEA_             |     | 15  |     | _20 |     | 30  | ns    | 24    |

| SE precharge time                           | t <sub>SEP</sub>  | 10  |     | 15  |     | 15  |     | ns    |       |

| SE pulse width                              | t <sub>SE</sub>   | 10  |     | 15  |     | 15  | _   | ns    |       |

| Serial data-out hold time after SC high     | <sup>t</sup> son  | 5   |     | 5   |     | 5   |     | ns    | 24    |

| Serial output buffer turn-off delay from SE | <sup>t</sup> SEZ  | 0   | 12  | 0   | 15  | 0   | 25  | ns    | 24    |

| Serial data-in setup time                   | t <sub>SDS</sub>  | 0   |     | 0   |     | 0   |     | ns    | 24    |

| Serial data-in hold time                    | <sup>t</sup> SDH  | 10  |     | 15  |     | 20  |     | ns    | 24    |

| SERIAL INPUT (Write) Enable setup time      | tsws              | 0   |     | 0   |     | 0   |     | ns    |       |

| SERIAL INPUT (Write) Enable hold time       | <sup>t</sup> swH  | 10  |     | 15  |     | 20  |     | ns    |       |

| SERIAL INPUT (Write) Disable setup time     | t <sub>swis</sub> | 0   |     | 0   |     | 0   |     | ns    |       |

| SERIAL INPUT (Write) Disable hold time      | <sup>t</sup> swiH | 10  |     | 15  |     | 20  |     | ns    |       |

#### **NOTES**

- All voltages referenced to Vss.

- 2. This parameter is sampled. Capacitance is calculated from the equation  $C = \underline{I\Delta t}$  with  $\Delta V = 3V$  and  $V_{CC} = 5V$ .

- 3. Icc is dependent on cycle rates.

- Icc is dependent on output loading. Specified values are obtained with minimum cycle time and the output open.

- 5. Enables on-chip refresh and address counters.

- The minimum specifications are used only to indicate cycle time at which proper operation over the full temperature range (0°C ≤ T<sub>A</sub> ≤ 70°C) is assured.

- 7. An initial pause of 100µs is required after power-up followed by any eight RAS cycles and 1 SC cycle before proper device operation is assured. The eight RAS cycle wake-up should be repeated any time the 8ms refresh requirement is exceeded.

- 8. AC characteristics assume  ${}^{t}T = 5 \text{ns}$ .

- VIH (MIN) and VIL (MAX) are reference levels for measuring timing of input signals. Transition times are measured between VIH and VIL (or between VIL and VIH).

- 10. In addition to meeting the transition rate specification, all input signals must transit between Vih and Vil (or between Vil, and Vih) in a monotonic manner.

- If CAS = Vih, DRAM data output (DQ1-DQ4) is high impedance.

- 12. If CAS = VIL, DRAM data output (DQ1-DQ4) may contain data from the last valid READ cycle.

- 13. DRAM output timing measured with a load equivalent to 2 TTL gates and 100pF. Output reference levels: VoH = 2.4V; VoL = 0.4V.

- 14. Assumes that <sup>t</sup>RCD < <sup>t</sup>RCD (MAX). If <sup>t</sup>RCD is greater than the maximum recommended value shown in this table, <sup>t</sup>RAC will increase by the amount that <sup>t</sup>RCD exceeds the value shown.

- 15. Assumes that  ${}^{t}RCD \ge {}^{t}RCD$  (MAX).

- 16. If CAS is LOW at the falling edge of RAS, DQ will be maintained from the previous cycle. To initiate a new cycle and clear the data out buffer, CAS must be pulsed HIGH for <sup>t</sup>CPN.

- 17. Operation within the <sup>t</sup>RCD (MAX) limit ensures that <sup>t</sup>RAC (MAX) can be met. <sup>t</sup>RCD (MAX) is specified as a reference point only; if <sup>t</sup>RCD is greater than the specified <sup>t</sup>RCD (MAX) limit, then access time is controlled exclusively by <sup>t</sup>CAC.

- 18. Operation within the <sup>t</sup>RAD (MAX) limit ensures that <sup>t</sup>RCD (MAX) can be met. <sup>t</sup>RAD (MAX) is specified as

- a reference point only; if <sup>t</sup>RAD is greater than the specified <sup>t</sup>RAD (MAX) limit, then access time is controlled exclusively by <sup>t</sup>AA.

- Either <sup>t</sup>RCH or <sup>t</sup>RRH must be satisfied for a READ cycle.

- 20. <sup>t</sup>OFF (MAX) defines the time at which the output achieves the open circuit condition and is not referenced to Voh or Vol.

- 21. tWCS, tRWD, tAWD and tCWD are restrictive operating parameters in LATE-WRITE, READ-WRITE and READ-MODIFY-WRITE cycles only. If  $^{t}WCS \ge {}^{t}WCS$  (min), the cycle is an EARLY-WRITE cycle and the data output will remain an open circuit throughout the entire cycle, regardless of  $\overline{TR}/\overline{OE}$ . If  $^{t}WCS \le {}^{t}WCS$  (MIN), the cycle is a LATE-WRITE and  $\overline{TR}/\overline{OE}$  must control the output buffers during the write to avoid data contention. If tRWD ≥ tRWD (MIN),  ${}^{t}AWD \ge {}^{t}AWD$  (MIN) and  ${}^{t}CWD \ge {}^{t}CWD$ (MIN), the cycle is a READ-WRITE and the data output will contain data read from the selected cell. If neither of the above conditions are met, the state of the output buffers (at access time and until CAS goes back to Vih) is indeterminate but the WRITE will be valid, if tOD and tOEH are met. See the LATE-WRITE AC Timing diagram.

- These parameters are referenced to CAS leading edge in early WRITE cycles and ME/WE leading edge in late WRITE or READ-WRITE cycles.

- During a READ cycle, if TR/OE is LOW then taken HIGH, DQ goes open. The DQs will go open with OE or CAS, whichever goes HIGH first.

- 24. SAM output timing is measured with a load equivalent to 2 TTL gate and 50pF. Output reference levels: VoH = 2.0V; VoL = 0.8V.

- 25. TRANSFER command means that  $\overline{TR}/\overline{OE}$  is LOW when  $\overline{RAS}$  goes LOW.

- 26. NONTRANSFER command means that  $\overline{TR}/\overline{OE}$  is HIGH when  $\overline{RAS}$  goes LOW.

- 27. LATE-WRITE and READ-MODIFY-WRITE cycles must have <sup>t</sup>OD and <sup>t</sup>OEH met (OE HIGH during WRITE cycle) in order to ensure that the output buffers will be open during the WRITE cycle. The DQs will provide previously read data if CAS remains LOW and OE is taken LOW after <sup>t</sup>OEH is met. If CAS goes HIGH prior to OE going back LOW, the DQs will remain open.

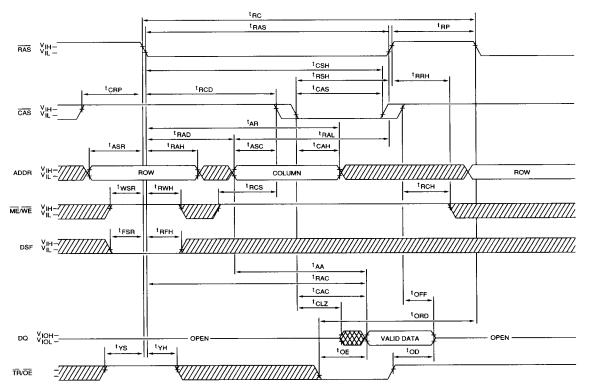

#### **DRAM READ CYCLE**

DON'T CARE

W UNDEFINED

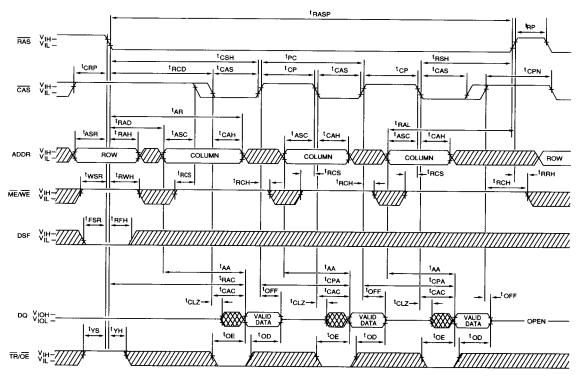

#### **DRAM FAST-PAGE-MODE READ CYCLE**

DON'T CARE

W UNDEFINED

NOTE: WRITE or READ-MODIFY-WRITE cycles may be mixed with READ cycles while in FAST PAGE MODE.

#### WRITE CYCLE FUNCTION TABLE

| LOGIC STATES |             |                 |                       |                                                            |  |  |

|--------------|-------------|-----------------|-----------------------|------------------------------------------------------------|--|--|